THE MARK-8 USER GROUP AS ALIVE AND RUNNING. IT'S ONLY 14 SEPT. AND WE ALREADY HAVE RECEIVED LETTERS FROM 30 PEOPLE. IT IS QUITE POSSIBLE THAT WE MAY END UP WITH HUNDREDS OF PARTICIPANTS. THIS ISSUE WILL INCLUDE A FEW THINGS THAT SEEM URGENT AND WELL SAVE THE GOOD THINGS FOR FUTURE ISSUES AFTER WE ACCUMULATE SOME MORE PARTICIPANTS.

- HOW DO YOU KEEP FROM PAYING \$120 FOR THE 8008 CHIEF?

- A. GET A SCHOOL DISCOUNT OF 20% FROM AN INTEL DISTRIBUTOR.

- B. TRY COOK, 25W178-39TH ST , NAPERVILLE, IL 60540 \$80 (P. 110 RE OCT)

- C. BEG RGS ELECTRONICS, 3650 CHARLES ST., SUITE K, SANTA CLARA, CA 95050 TO STOCK THEM AGAIN AT \$50. I GOT 2 FROM THEM BUT THEY SAY THEY ONLY HAVE ENOUGH LEFT FOR THEIR IK 8008 KIT. SEE P. 102 RE OCT AND 73 MAGAZINE P. 87 JUNE.

- D. TRY BILL GODBOUT ELECTRONICS, BOX 2673, OAKLAND AIRPORT, CA 94614 \$50, SEE AD IN 73 MAG. P. 87, JUNE 74.

- 2. HOW MANY BUGS ARE THERE IN THE CONSTRUCTION ARTICLE? A FEW HAVE SHOWN UP SO FAR. J. TITUS, THE AUTHOR MENTIONS THESE:

- A. CONNECTIONS ON BOTTOM OF BOARD ARE IN PARALLEL. ARRANGE BOARDS IN ORDER SHOWN IN BOOK AND WIRE. THEN CUT OUT WIRES BETWEEN CONTACTS 9 THRU 16 BETWEEN INPUT MUX AND ADDR/MANUAL BOARDS.

- B. ON PAGE 6, 4TH PARAGRAPH, LAST LINE, IT SHOULD READ "ON THE FOLLOWING INSTALL THE B JUMPERS AND RESISTORS R1-R4 AND R21."

- PLEASE REPORT ANY OTHER BUGS OR CONSTRUCTION PROBLEMS YOU FIND.

3. HOW DO YOU REMOVE AN IC FROM THE PC BOARDS WITHOUT REMOVING THE FOIL TOO? I GIVE UP, HOW? EVEN MOLEX IC SOCKET PINS ARE HAND TO USE ON THE MEMORY BOARDS. IF ONLY THE COMPLICATED FOIL PATTERNS COULD HAVE BEEN ON THE BOTTOM SIDE INSTEAD OF THE TOP SIDE OF THE BOARDS.

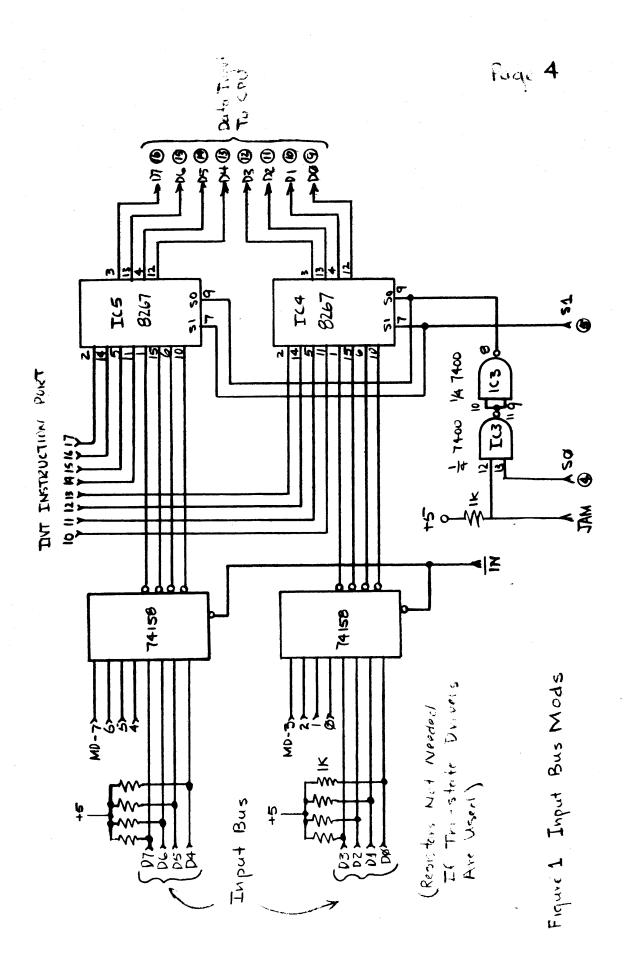

4. WHAT DO YOU DO IF YOU WANT MORE INPUT PORTS?

- A. USE J. TITUS/S BUS IDEA ON PAGE 9 AND 10.

- B. REWIRE THE INPUT MUX BOARD AS SHOWN IN FIG. 1 FOR AN INPUT BUS EITHER TRI-STATE OR WIRED-OR.

- C. IF YOU NEED MORE THAN 8 INPUT PORTS, TRY THIS. THE AC COMES OUT AT T1 OF MEM CYCLE 2 ON AN INP INSTRUCTION. I BELIEVE IT WILL BE LATCHED INTO IC-889. BY INCLUDING THE PROGRAMMING INSTRUCTIONS

- LAI (LOAD 1MMEDIATE)

- 15 (DEVICE NUMBER)

- INP B (PORT BEING MULTIPLEXED)

AND USING A 7442 OR <mark>74154 TO DECODE THE AC INFO, YOU CAN HAVE AS MANY</mark> INPUT PORTS AS YOU WANT. (MORE ABOUT THIS IN A FUTURE ISSUE.)

- 5. HOW DO I CONNECT A TELETYPE? A SCHEMATIC IS SHOWN IN FIG. 2.

- 6. HOW DO I BUILD A MODEM FOR A CASSETTE RECORDER? A GOOD QUESTION.

HERE ARE TWO UNTRIED PARTIAL CIRCUITS I'VE FOUND. IF ANYONE HAS BETTER INFORMATION, PLEASE GET IT TO US SO WE CAN DISTRIBUTE IT. THIS SEEMS TO BE EVERYONE'S TOP PRIORITY PERIPHERAL.

- 7. HOW CAN I GET HELP OR MORE INFORMATION ON CONSTRUCTING MY MARK-8 OR HELP IN DEBUGGING? HEAD OUT TO THE NEAREST ENGINEERING COLLEGE. EVERY ONE HAS A WHOLE BUNCH OF MICROPROCESSOR PROJECTS GOING ON AND CAN PROBABLY HELP YOU OUT WITH DEBUGGING, SOFTWARE, AND ROM PROGRAMMING, ETC. LET THE REST OF US KNOW WHAT YOU FIND OUT.

FAGE Z OF 8 PAGE 2 8. MHAI HAVE THE PARTICIPANTS SAID SO FAR? JIM FRY 18 DEVELOPING A CURSOR BOARD FOR TV TYPEWRITER WITH PROGRAM-MABLE CURSOR CONTROL AND IS TRYING TO IMPLEMENT AN ELABORATE INTERRUPT CAPABILITY.

GREG HUNTZINGER IS GOING TO USE THE MICRO-8 AND TV TYPEWRITER AS A FV TITLING SYSTEM FOR TV TAPING AND FOR COMPUTER ART.

ROBERT KELLY HAS 2 BAUDOT TTY'S HE WANTS INFO ON USING. K. A. MCGINNIS WANTS TO OBTAIN CHEAP WIRE WRAP SOCKETS. HE ALSO WANTS ' TO KNOW IF ANYONE IS INTERESTED IN BUILDING SOSO BASED COMPUTERS. IS ANYONE ELSE?

LAURENCE PLATE IS READY TO WRITE A BASIC AND WANTS TO INTERFACE A TRIG CALCULATOR

TERRY RITTER IS THE FIRST ONE TO SAY HIS MARK-8 IS RUNNING AND HAS SOME NEAT IDEAS ON PERIPHERALS.

LEE SORENSEN SAYS THE SCELBI-SH USER MANUAL (P. 101 RE OCT 74) IS VERY VALUABLE.

JONATHAN TITUS, THE MARK-S AUTHOR IS GOING TO CONTRIBUTE INFO ON A REMOTE INTERRUPT MODULE AND A 2102 RAM MEMORY. HE ALSO TELLS US THAT HE HAS A CALCULATOR INTERFACE ARTICLE SCHEDULED FOR RE IN THE NEXT COUPLE OF MONTHS.

UTER INSTALLATION FOR CABRILLO HIGH SCHOOL. WE PRESENTILY HAVE A 4K PDP8/E WITH A 32K DISK, OPTICAL MARK SENSE CARD READER, 2 TTY/S, A CENTRONICS 508 LINE PRINTER (DUE ANY DAY), A HOMEMADE PAPER TAPE READER AND FUNCH, HOMEMADE OSCILLOSCOPE GRAPHICS TERMINAL, AND A HOME-MADE SWITCH RELAY INTERFACE. WE WILL SOON BE EXPANDING TO A PDP-8/E ETOS 6 USER MULTILANGUAGE OS-8 TIME SHARE SYSTEM. WE WILL HAVE A COUPLE OF HOMEMADE 8008 SYSTEMS RUNNING SOON AND THE EE DEPARTMENT AT UNIV OF CA AT SANTA BARBARA IS INVESTIGATING THE POSSIBILITY OF LOANING US ONE OF THEIR VERY ELABORATE SOOS TRAINING SYSTEMS FOR EVALUATION IN THE HIGH SCHOOL ENVIRONMENT. WHAT CAN WE EXPECT FROM THE NEWSLETTER IN THE FUTURE? NOTHING!!! UNLESS YOU ARE WILLING TO CONTRIBUTE. I AM WORKING ON: 1) OBTAINING INFO ON SOFTWARE SOURCES. 2) GETTING PERMISSION TO RELEASE A BUNCH OF INFO FROM LAWRENCE RADIATION LABS. 3) A CONSTRUCTION ARTICLE ON MY SPECIALITY, \$75 HIGH SPEED PAPER TAPE READERS 4) A CONSTRUCTION WE NEED BADLY: 1) MODEM INFO FOR ARTICLE ON A SCOPE GRAPHICS TERMINAL. CASSETTE RECORDERS. 2) SOURCES OF TTY'S CHEAP. 3) INFO ON THE RELIA-BILITY OF VARIOUS DISCOUNT IC SUPPLIERS. 4) CIRCUITS FOR CONVERTING BAUDOT TO ASCIT AND VICE VERSA FOR CHEAP (TYTS: 5) MODIFICATIONS TO TV TYPEWRITER TO INCLUDE SCHROLLING. PLEASE CONTRIBUTE A FEW MINUTES OF YOUR TIME TO SEND IN ANYTHING THAT OTHER BUILDERS MIGHT BE INTER-

WHAT IS THE CABRILLO COMPUTER CENTER? WE ARE THE EDUCATIONAL COMPU-

6000 LUCK IN DEBUGGING AND MAY YOUR SOLDER BRIDGES BE FEW AND FAR BETWEEN. KEEP THOSE CARDS AND LETTERS COMING IN HAL SINGER MARK-8 USER GROUP EDITOR CABRILLO COMPUTER CENTER 4830 CONSTELLATION ROAD LUMEUC) UA 93436

ESTED IN DON'T LET THIS NEWSLETTER DIE LIKE SO MANY UTHERS HAVE

BECAUSE OF THE PARTICIPANTS RELUCTANCE TO CONTRIBUTE.

BILL ARNOLD 216 1/2 AVENUE B FORT DODGE, IOWA 50501

J. CALLAS 631 N. SAN PEDRO RD SAN RAFAEL, CA

CHARLES E. ECHARD 7820 JACKSON ROAD BEAUMONT, TX 77706

RUDOLF HAUSDORF 1961 REDONDO AVE. SALT LAKE CITY, UTAH 84108

ROBERT W. KELLEY 5806 MT TERMINAL DR. WACO, TX 76710

W. S. MILLER 2813 WGNER DR. BURLINGTON, NC 27215

LAURÊNCE L. PLATE 2320 SKYLINE WAY SANTA BARBARA, CA 93109

NOLEN F. ROBERSON 12511 JACKSON GRANDVIEW, MO 64030

JAMES UPCHURCH BOX 1987 SEBRING, FL 33870 ANGEL BRAVO 10333 FELSON ST. BELLFLOWER, CA 90706

JOSEPH A. CIMMINO 11 19304 RICHWOOD COURT BROOKEVILLE, MD

JIM FRY 4249 N. LOCKWOOD TOLEDO, OHIO 43612

LLOYD G. HANSON LAKELAND INSTR. LABS ANGOLA, INDIANNA 46703

WILLIAM R. MAINS 139 17TH ST. PASO ROBLES, CA 93446

R. W. MOELL 5505 DAYWOOD CT. RALEIGH, NC 27609

RADIO-ELECTRONICS SUITE 1105 200 PARK AVE. SOUTH NEW YORK, NY 10003

LEE L. C. SORENSON 10226 VICTOR1A AVE WH1TTIER, CA 90604 RICK BRENNON 601 SOUTH KNIGHT PARK RIDGE, IL 60068

PAGE 3 OF 8

M. WYMORE EDWARDS, SPANGLER, WYMORE & KLAAS 1700 BROADWAY DENVER, CO 80202

0. F. HAMM 4751 LOUISIANA AVE. ST. LOUIS, MO 63111

GREG HUNTZINGER 2332 OAKLAND ST. AURORA, CO 80010

K. A. MCGINNIS P. U. BOX 1287 SAN MATEO, CA 94401

CABELL A. PEARSE 3523 TILDEN ST. N.W. WASHINGTON D.C. 20008

TERRY RITTER DIRECTIONAL ANTENNA CO. 2524 GLEN SPRINGS WAY 78741

JONATHAN A. TITUS TITUS LABS P. O BOX 242 BLACKSBURG, VA 24060

9 67 SERIAL DATA OUT KERIAL DATAIN Š 57 #23 Transmiffer Duz Strobe - Lenters data into transmitter buffer-such as keyboard strobe, processor output port strobe etc. #35 H No Parity #39 L Odd Parity #39 H Even Parity Connect pins to Gad for L; to VCC for H, through 10K, R-5 (Hardwire, use on board switchs, bring to control panel direct, or use gates) 2 202 25 500 20 2 3 5 #371, #381, 6 #371, #38 H 7 #37H, #381, 8 #37H, #39H TVT orMICRCPRCCESSOR DATA CUT 11016 8 2 CCM 2502 UNIVERSAL ASYNCHRONOUS RECEIVER/TRANSMITTER LSB to pin#26, MSB to #33 TRANSMITTER CLOCK 34 36 35 39 30 37 RECEIVER CLOCK Pin # 36 L One Stop Bit H Two Stop Bits ADDITIONAL IC'S MIGHT BE NEEDED TO CUSTOMIZE UART CIRCUIT TO INDIVIDUAL NEEDS (OR gades: inverters, etc.) 851 40 DATA STROBE 6120 22 28

Interface Circuits

to tape recorder

PARITY

No. of Data Bits

interface or to

RS-232-C

TTY Keyboard

Loop current is to be provided by the attached Teletype, etc. GND to disable 300 T.P. MAX 2N3643 PHYSICAL DIMENSIONS

TO-105

TO-105 #21 Master Raset, needs to be pulsed high after system turn on( to be controlled by system initialize)

#18 RDA, (Tri-state) is H when data is avavailable at receiver(#5-#12)

#18 RDA a L clears the RDA flag

#4 RDE when brought o L.

#19 #19 #19 #19 #19 for visual indicators, or software messages to processor)

#13, #14, #15 are error flags (for visual indicators, or software messages to processor)

#16 When at L, enables above, RDA, TMBT, and would normally be tied to ground Echo END OF CHARACTER TRANSMITTER BUFFER EMPTY \*NOTE-Normal supply voltages, VCC, #1, 5V, VDD, #2, -12V, Gnd, #3. VDD may be -9 if Baud rate doesn't exceed 10K ( normal uses it won't) and strobes are in the order of 1 us. Clock rate (output of 555, pin #3) should be adjusted to 16 X the desired beat rate, and is connected to UAT pins #1; #40 if the preceiver and transmitter are to be operated at the same Baul rate. Cf course, if additional Baud rates are desire arrange for additional 553's or to switch timing components. DATA TO TVT OR MICROPHOCESSOR Input Bus (Tri-State-nyllgad Baud rate should be adjusted to 16 X LSB to pin #12, MSB to # 5 R 1-51 K 1/4 W \*\*\* R 2- 50K Pot \*\*\* R 3, 4 1K 1/4W R 5, 6, 7 10K 1/4 W K <, 9 150 ohm 1/4 W

(12B, 10C, 9E, etc. refers either to pin number on 75450 or base, collector, and emitter of transistor.)

IC 6-7404 /7408 if idea gating of inversion desired

second clock rate,

555 (for a

Cptional

IC 2- COM 2502 or other standard UART IC 5- 7400 -when used

with Q 1. Q2 Otherwise 75450

- 2N3643 or 2N2222

or other NPN

PAGE

TTY Common

88 ş

ž

807

PO PO

EER

108

400 8

7210-4

v

TTY Printer

. st

8JTTIM3

3S**V**8

016 019 018 018

901 112

325 DIA

COLLECTOR

Figure Connection 2 TTY

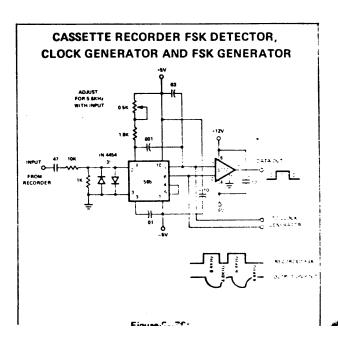

#### FSK DATA CONVERTER FOR CASSETTE RECORDER

A circuit scheme which allows an ordinary reel or cassette tape recorder to be used as a digital data recorder was submitted by Daniel Chin of Burlington, Massachusetts.

"The circuit design allows any single-track audio tape recorder with frequency response to 7kHz to be used as a digital recorder for many non-critical applications. This application provides a complete data recording system using two recorded frequencies on a single track. The two frequencies are obtained from two synchronized NE565s. Detection of the recorded frequencies requires a third NE565. A fourth circuit is used to generate and synchronize the system clock. The advantages obtained by using these techniques are elimination of the need for:

- 1. A timing channel to strobe off the data, or

- A third frequency for null, while using the other two frequencies for 1 and 0.

This implementation, therefore, is one of the simplest ways to get a digital recording system on an audio recorder. It is shown in block diagram form in Figure 8—75.

The parameters chosen for the circuit design allow a digital recording bit rate of 800Hz or 100 8-bit characters per second. Though 100 characters per second is less than the 300-character-per-second speed of a high-speed paper tape reader, the low cost of this circuitry combined with the audio tape recorder should make this system very attractive from a cost performance viewpoint. This is especially true when compared with the normal Teletype speed of 10 characters per second.

BLOCK DIAGRAM OF

PLL CASSETTE RECORDER

PLAY

TAPE

RECORDER

RECORDER

RECORDER

RECORDER

125mS

DATA IN

125mS

The circuits will also work with the readily available low cost cassette recorders now available, which make compact as well as low cost information storage. A FSK system of recording is used, which allows the voice recording and reproduction electronics of the recorder to be unmodified for use in recording digital information. The retained electronics may also be used to record voice message identification of the various sections of the tape.

The intended use of this circuit is to convert an audio recorder for minicomputer programs written for engineering design applications. Such an application requires good information storage and retrieval over a wide range of storage time. Redundancy may be incorporated by using a two-channel recorder (stereo) and a FSK detector per channel. The outputs of the two detectors could then be ORed digitally to recovered recorded 1s and, thus, give a safeguard against dropouts.

### Circuit Description

Four NE565s are used in three circuits to achieve the design. These are:

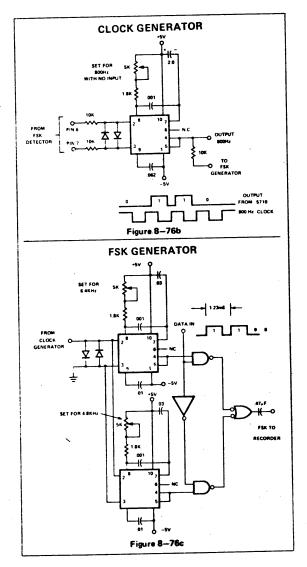

The FSK detector (Figure 8–76a) is used to detect 6.4kHz for a 1 and 4.8kHz for a 0. The data output is taken from a 5711 connected to pins 7 and 6 of the NE565. The recording method used is RZ FSK, which means that a zero is recorded as 4.8kHz for the entire bit period and one is recorded as 6.4kHz for about 60 percent of the period and 4.8kHz for the remaining 40 percent of the period. This 60 percent bit duty cycle insures that the clock will synchronize with a negative transition during the time that a 1 should be detected.

The clock generator (Figure 8–76b) is used to derive the 800Hz with no input. When the data pulses are extracted from the recorded data, the clock is synchronized to the data. The design allows up to 7 zeros in succession without causing the clock to go out of synchronization. This condition is easily met if odd parity is used to record the 8-bit characters. (One of the 8 bits is a parity bit and, thus, one bit out of 8 is always a one.)

The FSK generator (Figure 8–76c) provides the FSK signal for recording on tape. It consists of 2 oscillators locked to the basic 800Hz system clock but oscillating at 6.4kHz and 4.8kHz. The incoming data to be recorded selects either oscillator as the frequency to be recorded. Harmonic suppression of the square wave output is taken care of automatically by the high frequency roll off characteristic of the tape recorder."

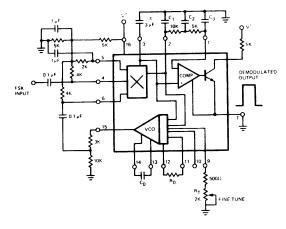

filter is formed by connecting a capacitor or an RC network from pin 2 to ground, as shown in Figure 16. The resulting filter transfer functions are also shown in the figure where  $R_1$  ( = 6 k $\Omega$ ) is the internal impedance at pin 2. In this application, pin 3 is ac grounded through a bypass capacitor,  $C_B$ , to insure proper ac bypass  $(C_B \geq 10\ C_1)$ .

In high frequency applications ( $f_0 > 100 \text{ kHz}$ ) for FM demodulation, tone detection and frequency synthesis, it is recommended that pin 3 not be bypassed but connected to ground through a low-pass filter identical to that used at pin 2 (See Figures 22 and 23).

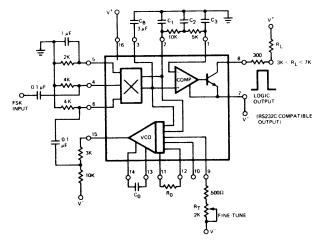

Figure 17. Circuit Connection For FSK Demodulation (Single Supply)

Figure 18. Split-Supply FSK Demodulation with RS232C Compatible Output

# APPLICATIONS INFORMATION

## **FSK DEMODULATION**

Figures 17 and 18 show a generalized circuit connection for FSK demodulation. The circuit is connected as a PLL system by ac coupling the VCO output (pin 15) to pin 6. The FSK input is applied to pin 4. When the input frequency is shifted, corresponding to a data bit, the polarity of the dc voltage across the phase detector outputs (pins 2 and 3) is reversed. The voltage comparator and the logic driver section convert this dc level shift to a binary pulse. One of the phase detector outputs (pin 3) is ac grounded and serves as the bias reference for the voltage comparator section. Capacitor C<sub>1</sub> serves as the PLL

loop filter, and  $C_2$  and  $C_3$  as post-detection filters. The timing capacitor,  $C_0$ , and the fine-tune adjustments are used to set the VCO frequency,  $f_0$ , midway between the "mark" and "space" frequencies of the input signal. Typical component values for 300 baud (103-type) and 1200 baud (202-type) MODEM applications are listed below:

| OPERATING<br>CONDITIONS                                         | TYPICAL COMPONENT VALUES                                                                                                                            |

|-----------------------------------------------------------------|-----------------------------------------------------------------------------------------------------------------------------------------------------|

| 300 Baud                                                        |                                                                                                                                                     |

| Low Band: $f_1 = 1070 \text{ Hz}$<br>$f_2 = 1270 \text{ Hz}$    | $R_0 = 5.1 \text{ k}\Omega, C_0 = 0.22 \mu\text{F}$<br>$C_1 = C_2 = 0.047 \mu\text{F},$                                                             |

| High Band: $f_1 = 2025 \text{ Hz}$<br>$f_2 = 2225 \text{ Hz}$   | $C_3 = 0.033 \mu\text{F}, C_4 = 3 \mu\text{F}$ $R_0 = 8.2 k\Omega, C_0 = 0.1 \mu\text{F}$ $C_1 = C_2 = C_3 = 0.033 \mu\text{F}$                     |

| 1200 Baud<br>$f_1 = 1200 \text{ Hz}$<br>$f_2 = 2200 \text{ Hz}$ | $R_0 = 2 \text{ k}\Omega, C_0 = 0.14 \mu\text{F}$ $C_1 = 0.033 \mu\text{F}, C_3 = 0.02 \mu\text{F}$ $C_2 = 0.01 \mu\text{F}, C_4 = 0.1 \mu\text{F}$ |

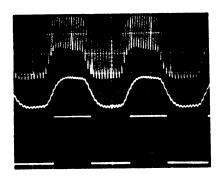

Figure 19. Demodulated Waveforms for 150 Baud Data Rate,  $f_1 = 1070 \text{ Hz}$ ,  $f_2 = 1270 \text{ Hz}$

Top: Pin 2

Center: Pin 1

Bottom: Pin 8

0.5 V/div.

5.0V/div.

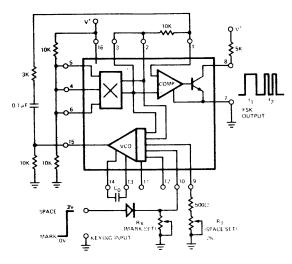

Figure 20. Circuit Connection For FSK Generation (<100kHz)

Figure 19 shows typical waveforms at different points in the circuit for a 150 baud data rate with "mark" and "space" frequencies of 1270 and 1070 Hz respectively. The top waveform is the phase detector output at pin 2; the middle waveform is the filtered signal at the comparator input (pin 1), and the bottom waveform is the logic output at pin 8.

RS-232C COMPATIBLE OPERATION (See Figure 18): For split-supply operation, the logic output section can function as a line-driver circuit, compatible with RS-232C specifications. This can be achieved by connecting a 300 $\Omega$  series resistance to pin 8, and choosing a pull-up resistor R<sub>L</sub> in the range of 3 K $\Omega$  to 7 K $\Omega$ .

ENABLE/DISABLE CONTROLS: In FSK demodulation applications, the operation of the circuit can be "inhibited" by applying a disable logic signal to either pins 2, 3 or 5. Application of a negative inhibit pulse to pin 3 introduces a dc offset across the comparator inputs and sets the logic output (pin 8) to a "high" state. If the same pulse is applied to pin 2, then a "low" state occurs at pin 8. Applying either a 3-volt positive or negative "inhibit" pulse to pin 5 disables the phase detector section, and sets the logic output to a "low" state. The enable/disable controls are particularly useful when using the XR-210 in a carrier-level detection system. Here the circuit can be activated only when the input signal exceeds a pre-set threshold value.

### **FSK GENERATION**

A typical circuit connection for this application is shown in Figure 20. The coarse setting of the frequency is determined by the choice of  $C_0$  across pins 13 and 14. Normally,  $C_0$  is chosen to give a free running frequency,  $f_0$ , approximately 5% lower than the "space" frequency,  $f_1$ . Then, the "space" and "mark" frequencies  $f_1$  and  $f_2$  are set by the choice of resistors  $R_T$  and  $R_X$  as:

$$f_1 = f_{\text{space}} = f_0 \left( 1 + \frac{0.1}{R_T} \right)$$

Hz

$$f_2 = f_{mark} = f_1 \left( 1 + \frac{0.3}{R_X} \right)$$

Hz

where the resistor values are in  $k\Omega$ . "Space" frequency is set prior to the "mark" frequency with the selection of  $C_0$  and the fine-tune resistor,  $R_T$ , with pin 10 open circuited. "Mark" frequency is then determined by the appropriate choice of  $R_X$  from pin 10 to ground.

The VCO output available at pin 15 is a symmetrical square-wave with a 2.5  $V_{p-p}$  output amplitude. The duty cycle asymetry of the VCO output is typically less than 2%.

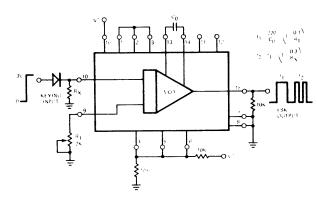

Figure 21. High Frequency FSK Generation Using VCO Section Only